- ATX7006

- Home

- Overview

- Development

- Software

- Hardware

- Articles

- Static characterization

- 1. ADC transition points

- 2. ADC parameter calculations

- 2. DAC parameter calculations

- 4. ATX7006

- Articles & Information

- FAQ overview

- Online Command Reference

- Static characterization

- Dynamic characterization

- ADC Histogram test

- DAC frequency response

- Terms ADC & DAC

- Application notes

- Application notes overview

- ADC test setup

- Reference current DAC

- Characterization 16 bit ADC

- Contact

- Contact

3. Parameter calculations D/A converter

The linearity parameter calculations (INLE, DNLE, etc.) of a D/A converter are based on the output voltages of the device. The output voltages of a D/A converter can be measured by applying the digital codes to the input of the device.

The following parameters will be discussed:

DAC Examples

To explain the linearity parameters of an D/A converter, the plot below can overlay some example DAC devices with an ideal 4 bits DAC. The plot can show five different kinds of DAC data:

- 1) DAC 1: a DAC with only an offset error

- 2) DAC 2: a DAC with only a gain error

- 3) DAC 3: a DAC with an offset, gain and linearity error, monotonic

- 4) DAC 4: a DAC with an offset, gain and linearity error, non-monotonic

- 5) Random DAC data: random errors. Use the button "New DAC data" for a new DAC

Loading... (javascript must be enabled)

Click on a point

The following DAC data presentations are available:

- Transfer plot: The transfer plot of the ideal DAC and example DAC (blue line) are overlayed

- End point overlay: Overlay end point line and DAC error related to the end point line (blue line)

- Best fit overlay: Overlay best fitting line and DAC error related to the best fitting line (blue line)

- End point error: The error of the example DAC compared to the end point reference line (error in LSBs)

- Best fit error: The error of the example DAC compared to the best fitting reference line (in LSBs)

- Differential error: The error of each step of the example DAC (LSBs)

- Total unadjusted error: The error of the example DAC compared to the ideal line(in LSBs)

The Differential error (6) shows the error in of each step.

For the first three presentations, the y-axis shows (DAC output) voltages or LSBs and the x-axis (DAC input) codes. For the other 4 presentations the y-axis shows the error in LSBs.

Parameter calculations

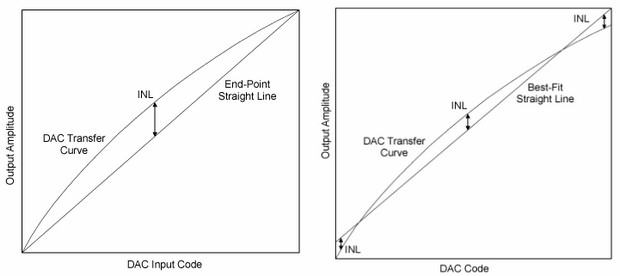

End Point and Best Fitting line

Similar to the ADC error parameter calculations, it is necessary to have a reference line for the parameter calculations. Also the same reference lines are used:

- End point line

- Best fitting line

The end point line is a straight line between the first output voltage and the last output voltage. So only the first and last measured voltages are used for the calculation of the reference line. The first and last voltage of the end point error plot will always be zero.

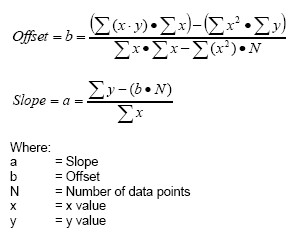

The best fitting line calculation uses all voltages. Also here, the least-squares linear regression algorithm is used. For the completeness, again the equation of the best fitting line (y = ax + b):

Offset Error

The output voltage when the digital input code (mostly 0 or halve scale) is set to give an ideal output voltage of 0 V (end point calculation). For the best fitting line calculation the offset error is the offset of the best fitting reference line related to the ideal transfer line.

Examples:

DAC 1: The output voltage at code 0 starts 0.5 LSB (0.15 V) above 0 V. The offset error is 0.5 LSB.

DAC 2: The output voltage at code 0 starts at 0 V. The offset error is 0 LSB.

DAC 3: The output voltage at code 0 starts below 0V. It has a negative offset of -0.25 LSB for the end point presentation. The best fit reference line starts 1.41 LSB below 0V, see the best fit overlay presentation (3). The best fit offset error is -1.41 LSB.

DAC 4: The output voltage at code 0 starts 0.25 LSB above 0V. The end point offset error is 0.25 LSB. The best fit line starts 1.10 LSB above 0V (select best fit overlay (3) presentation). The best fit offset error is 1.10 LSB.

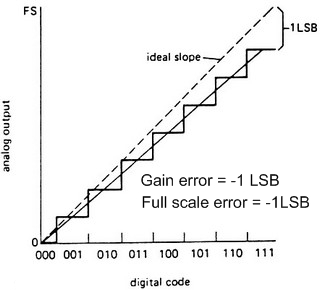

Full scale error

The full scale error is the error of the full scale output voltage (maximum input code) from the ideal full scale output voltage (end point full scale error). It is equal to the sum of the gain error and offset error.

Examples:

DAC 1: The output voltage at code maximum code (code 15) is 0.5 LSB (0.15 V) above full scale voltage (4.5 V). The full scale error is equal to the offset error (0.5 LSB).

DAC 2: The output voltage at code maximum code (code 15) is 0.75 LSB below the full scale voltage (4.5 V). The full scale error is equal to the gain error (-0.75 LSB).

DAC 3: The output voltage at code maximum code is 0.45 LSB above full scale voltage. The end point full scale error is -0.25 LSB + 0.70 LSB = 0.45 LSB. The best fit reference line ends at 0.43 LSB below full scale, see the best fit overlay presentation (3). The best fit full scale error is -1.41 LSB + 0.98 LSB = -0.43 LSB.

Gain error

The gain error is equal to the Full scale error with the offset error subtracted. It is the deviation (of the end point or best fit reference line) from the ideal slope of the transfer characteristic. The slope can be found in the "a" of the reference line y = ax + b. The gain error can be calculated with the equation (a - 1)(N-1). Where N is the number of converter steps.

Examples:

DAC 1: has not gain error, (1 - 1)(16-1) = 0.

DAC 2: see full scale error, (0.95 - 1)(16 - 1) = -0.75 LSB

DAC 3: The end point full scale error is 0.45 LSB. The gain error is 0.45 - -0.25 LSB = 0.7 LSB or (1.0467 - 1)(16 - 1) = 0.7 LSB. The best fit reference line ends at 0.43 LSB below full scale, see the best fit overlay presentation (3). The best fit full scale error is -0.42 LSB. The gain error is -0.43 LSB - -1.41 LSB = 0.98 LSB or (1.0653 - 1)(16 - 1) = 0.98 LSB.

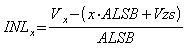

Integral non linearity error (INL/INLE)

Integral non linearity error describes the departure from a reference line. This reference can be an end point line or best fitting line. It is a measure of the straightness of the transfer function and can be greater than the differential non-linearity. The size and distribution of the DNL errors will determine the integral linearity of the converter. The INL error is calculatated by:

Where V(x) is the output voltage at input code x. Vzs is the zero scale voltage of the reference line. ALSB is the actual (or measured) LSB step. The actual LSB step is calculated by ILSB/a , where ILSB is the ideal LSB step and "a" is the angle of the reference line (the "a" of y = ax + b).

INL is a static specification and relates to THD (a dynamic specification). However, distortion performance can not be predicted from the INL specification, except to say that THD tends to become worse as INL departs from zero.

Examples:

For an INL plot, select the Best fit error (4) or End point error (5) presentation. The maximum deviation from the zero line (the zero line is the reference line) is the INL error.

DAC 4: Select the Best fit error plot (5) or end point error plot (4). The maximum deviation is at code 6. The end point INL error is 2.06 LSB, the best fit INL error is 1.64 LSB.

DAC 1 does only have an offset error, the INL error is zero.

DAC 2 does only have a gain error, no linearity error.

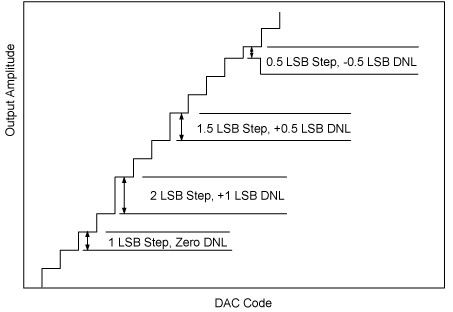

Differential non linearity error (DNL/DNLE)

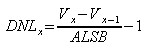

The maximium deviation of the 1 LSB step. For an ideal DAC the two adjacent digital codes correspond to an output voltage that are exactly 1 LSB apart. The 1 LSB step for the DNL calculation is based on the measured (or actual) LSB step. The actual 1 LSB step is the ideal LSB multiplied by "a" (ILSB x a) where "a" is the angle of the reference line (the "a" of y = ax + b). In reality the difference between the actual 1 LSB (1 x a) and the ideal 1 LSB step is very small. The DNL is calculated by:

Where ALSB is the actual 1 LSB step. Vx is the output voltage at input code x and V(x-1) is the output voltage at input code x-1.

A DNLE less than -1 lsb will lead to a non-monotonic transfer function. DAC 4 is lowering in output voltage at code 7. In the differential error presentation (6), an error of 2.12 LSB can be found.

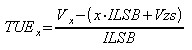

Total unadjusted error (TUE)

Total Unadjusted Error is a specification that includes linearity errors, gain error, and offset error. It is the worst-case deviation from the ideal device performance. The TUE is calculated by:

Where V(x) is the output voltage at input code x. Vzs is the zero scale voltage of the (ideal) DAC (usually 0V). ILSB is the ideal LSB step.

Select the Total unadjusted error presentation (7) for the TUE. In fact the blue line in the transfer presentation (1) is also a total unadjusted presentation.

<< Previous (2. Parameters calculations A/D converter) Next >> (4. Linearity calculations on the ATX7006)